## 5MSPS 4 通道网络实时采集卡

- 1. FPGA+ARM 架构+低速 4 路同步 5MSPS AD 采集系统, arm 为双核 1G 主频, fpga 为 Xilinx xc7z020, ddr3 内存 1g。

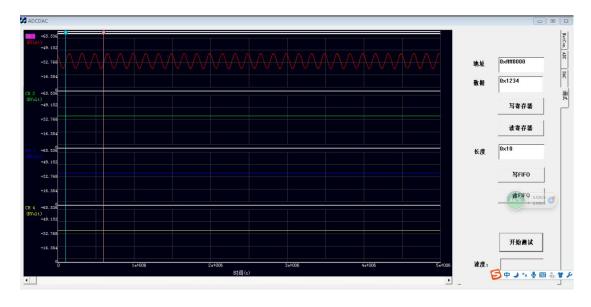

- 2. 单通道 A/D 采集要求:通道 AD 为 12 位,输入耦合 dc,采样速率最高为 5MSPS,信号输入范围正负 5V。4 通道同步采样。模拟量输入接口:参考甲 方样品,弯脚绿端子(间距 5.08mm 带固定点),为单端采集。

- 3. 可进行连续采集、门限触发采集(正负门限)、延时触发采集(延时范围 0us-1s),其中门限触发采集的触发条件和触发点前后的采集点数可设置。无论何种采集方式,每次读取一定长度的 A/D 数据,必须给出第一个采样点的 GPS 时间(年、月、日、时、分、秒、毫秒、微秒、纳秒)。 GPS 接口:参考 甲方样品,弯脚绿端子(间距 3.81mm 带固定点)。

- 4. 板卡带同步时钟接口,可多块板卡同步采集,支持 GPS 秒脉冲同步

- 5. 对外串口:信号包括 RS232 的收发地及+12V 电源,12V 电源是可控制的,通过高速采集板主板 CPU 控制关断,提供 LINUX 驱动支持。参考甲方样品,弯脚绿端子(间距 3.81mm 带固定点)。

- 6. 以太网口: 千兆以太网口。

- 7. USB 接口: 1 个, 支持鼠标及 U 盘。

- 8. 开放 arm 下位机 qt 应用源码和上位机 dll 动态库 c++源码及网口通讯协议, 提供 arm 下位机 qt 和上位机 c++测试程序,测试板卡上述功能,并提供源码。

- 9. 外形尺寸为: 160mmx110mmx40mm。